## **ST. LAWRENCE HIGH SCHOOL**

A Jesuit Christian Minority Institution

## WORKSHEET - 40

| <b>Topic: Inntroduction and adder circuits</b> |                                                              |                            |                                              |

|------------------------------------------------|--------------------------------------------------------------|----------------------------|----------------------------------------------|

| Subject: COMPUTE                               | R SCIENCE                                                    | Class - 11                 | F.M:15                                       |

| Chapter: Combination                           | onal logic Circuit                                           |                            | Date: 27/02/2021                             |

| Choose                                         | the correct                                                  | answer for each qu         | lestion: [5 X 1 = 15]                        |

|                                                |                                                              | nents of combinational of  |                                              |

|                                                | a. Input var                                                 | riables                    |                                              |

|                                                | b. Logic gat                                                 | es                         |                                              |

|                                                | c. Output v                                                  | variables                  |                                              |

|                                                | d. All of the                                                | ese                        |                                              |

| 2. H                                           | ow many half a                                               | dders are required to co   | nstruct a full adder?                        |

|                                                | a. 0                                                         |                            |                                              |

|                                                | b. 1                                                         |                            |                                              |

|                                                | c. 2                                                         |                            |                                              |

|                                                | d. 3                                                         |                            |                                              |

| 3. At                                          | t any instant of                                             | time, the output of the _  | depends only on the present                  |

| in                                             | put terminals.                                               |                            |                                              |

|                                                | a. Combina                                                   | •                          |                                              |

|                                                | b. combina                                                   |                            |                                              |

|                                                | c. combifor                                                  |                            |                                              |

|                                                | d. combidig                                                  |                            |                                              |

|                                                |                                                              | etween half adder and fu   |                                              |

|                                                |                                                              | two inputs while full ad   | -                                            |

|                                                |                                                              | s one output while full ac |                                              |

|                                                |                                                              | two inputs while full add  | der has three inputs                         |

| •                                              | All of the Men                                               |                            |                                              |

|                                                |                                                              | contains                   |                                              |

|                                                | 3 combination                                                | -                          |                                              |

| ,                                              | 4 combination                                                | •                          |                                              |

| -                                              | 6 combination                                                | •                          |                                              |

| -                                              | 8 combination                                                | •                          |                                              |

|                                                |                                                              |                            | then the carry is given by                   |

| -                                              | a) A AND B OR (A OR B) AND C<br>b) A OR B OR (A AND B) C     |                            |                                              |

|                                                | •                                                            | AND B) C                   |                                              |

| -                                              | c) (A AND B) OR (A AND B)C<br>d) A XOR B XOR (A XOR B) AND C |                            |                                              |

|                                                | •                                                            |                            | an an inclution of full colder?              |

|                                                | -                                                            | UK and EXUK gates are r    | equired for the configuration of full adder? |

| a)                                             | 1, 2, 2                                                      |                            |                                              |

|                                                |                                                              |                            |                                              |

|                                                |                                                              |                            |                                              |

- b) 2, 1, 2

- c) 3, 1, 2

- d) 4, 0, 1

- 8. If A and B are the inputs of a half adder, the carry is given by \_\_\_\_\_

- a) A AND B

- b) A OR B

- c) A XOR B

- d) A EX-NOR B

- 9. Half-adders have a major limitation in that they cannot \_\_\_\_\_\_

- a) Accept a carry bit from a present stage

- b) Accept a carry bit from a next stage

- c) Accept a carry bit from a previous stage

- d) Accept a carry bit from the following stages

- 10. If A and B are the inputs of a half adder, the sum is given by \_\_\_\_\_

- a) A AND B

- b) A OR B

- c) A XOR B

- d) A EX-NOR B

- 11. In which operation carry is obtained?

- a) Subtraction

- b) Addition

- c) Multiplication

- d) Both addition and subtraction

- 12. If A, B and C are the inputs of a full adder then the sum is given by \_\_\_\_\_

- a) A AND B AND C

- b) A OR B AND C

- c) A XOR B XOR C

- d) A OR B OR C

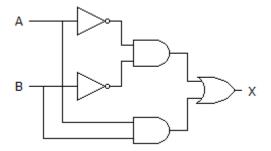

- 13. Which of the following logic expressions represents the logic diagram shown?

- a) X=AB'+A'B

- b) X=(AB)'+AB

- c) X=(AB)'+A'B'

- d) X=A'B'+AB

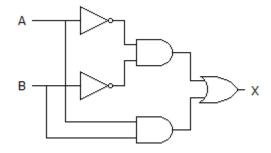

14. What type of logic circuit is represented by the figure shown below?

- a) XOR

- b) XNOR

- c) AND

- d) XAND

15. Total number of inputs in a half adder is \_\_\_\_\_

- a) 2

- b) 3

- c) 4

- d) 1

Phalguni Pramanik